|

На данной странице представлена ознакомительная часть выбранного Вами патента

Для получения более подробной информации о патенте (полное описание, формула изобретения и т.д.) Вам необходимо сделать заказ. Нажмите на «Корзину»

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И - ИЛИ - НЕ |  |

Номер публикации патента: 2166837 |  |

| Редакция МПК: | 7 | | Основные коды МПК: | H03K019/18 H03K019/20 | | Аналоги изобретения: | ШУР М. Современные приборы на основе арсенида галия. - М.: Мир, 1991, с. 472. RU 2115998 С1, 20.07.1998. RU 2094944 С1, 27.10.1997. EP 0476341 А1, 22.08.1991. |

| Имя заявителя: | Таганрогский государственный радиотехнический университет | | Изобретатели: | Коноплев Б.Г.

Рындин Е.А. | | Патентообладатели: | Таганрогский государственный радиотехнический университет |

Реферат |  |

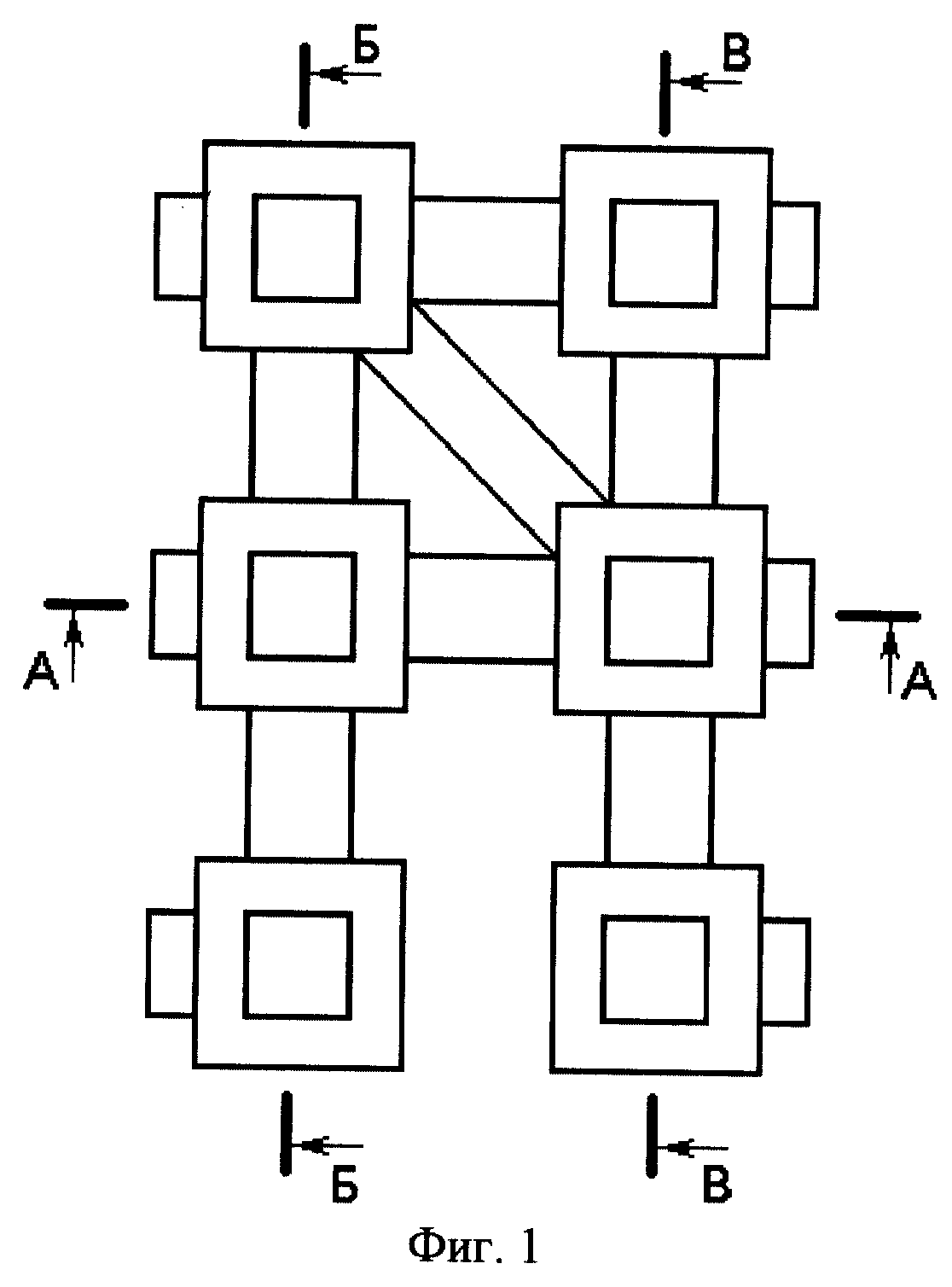

Изобретение относится к вычислительной технике и интегральной электронике, а более конкретно - к интегральным логическим элементам СБИС и, в частности, к логическому элементу И-ИЛИ-НЕ на комплиментарных нормально закрытых полевых транзисторах с управляющими переходами Шоттки. Для сокращения занимаемой площади, повышения быстродействия, уменьшения потребляемой мощности и энергии переключения в интегральный логический элемент, содержащий области стоков, истоков и каналов четырех транзисторов второго типа проводимости, металлические затворы Шоттки транзисторов второго типа проводимости, четыре входные металлические шины, соединенные с затворами Шоттки транзисторов второго типа проводимости, выходную металлическую шину, соединенную со стоковыми областями первого и третьего транзисторов второго типа проводимости, слоя разделительного диэлектрика, металлическую шину нулевого потенциала, металлическую шину питания, введены полупроводниковая подложка второго типа проводимости, являющаяся совмещенной истоковой областью второго и четвертого транзисторов второго типа проводимости и соединенная по всей свободной поверхности с металлической шиной нулевого потенциала, области стоков, истоков и каналов четырех транзисторов первого типа проводимости, металлические затворы Шоттки транзисторов первого типа проводимости, соединенные с входными металлическими шинами, металлическая шина, соединенная с областями первого типа проводимости, являющимися истоками шестого и восьмого и стоками пятого и седьмого транзисторов первого типа проводимости, полупроводниковая подложка первого типа проводимости, являющаяся совмещенной истоковой областью пятого и седьмого транзисторов первого типа проводимости и соединенная по всей свободной поверхности с металлической шиной питания, причем транзисторы выполнены в виде двух призм с квадратными основаниями, каждое из которых имеет площадь, равную площади одного контактного окна, при этом каждая призма содержит по два транзистора второго типа проводимости и по два транзистора первого типа проводимости, расположенных друг над другом и имеющих вертикальную ориентацию каналов, металлические затворы Шоттки имеют кольцеобразную форму, длины каналов транзисторов определяются толщиной металлических затворов, металлические шины расположены в девяти слоях, изолированных слоями разделительного диэлектрика, причем входные металлические шины расположены в тех же слоях, что и полупроводниковые области транзисторов. 4 ил.

|