|

На данной странице представлена ознакомительная часть выбранного Вами патента

Для получения более подробной информации о патенте (полное описание, формула изобретения и т.д.) Вам необходимо сделать заказ. Нажмите на «Корзину»

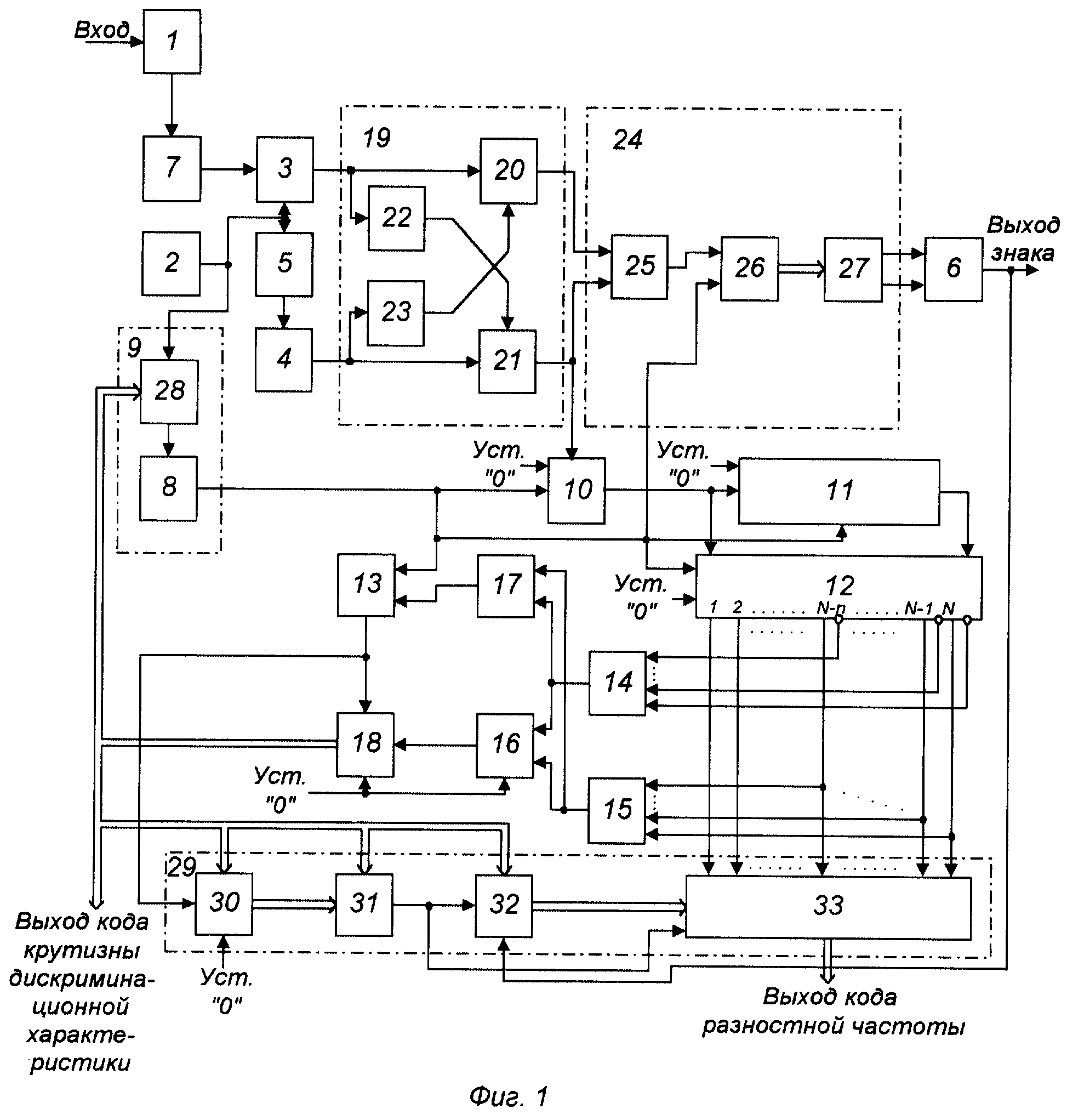

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР |  |

Номер публикации патента: 2166773 |  |

| Редакция МПК: | 7 | | Основные коды МПК: | G01S013/58 H03D013/00 | | Аналоги изобретения: | RU 2040852 C1, 27.07.1995. RU 94004572 A1, 20.03.1996. US 3688201, 29.08.1972. EP 03132206 A2, 26.04.1989. |

| Имя заявителя: | Таганрогский государственный радиотехнический университет | | Изобретатели: | Литюк В.И.

Ярошенко А.А. | | Патентообладатели: | Таганрогский государственный радиотехнический университет |

Реферат |  |

Изобретение относится к радиотехнике и может использоваться в радиолокационных и связных системах для измерения частоты непрерывного или амплитудно-модулированного радиосигнала, принимаемого на фоне шумов. Для увеличения помехоустойчивости, что и является достигаемым техническим результатом, более полного использования элементов памяти устройства во всех режимах обработки сигнала и для возможности адаптивного изменения крутизны и формы дискриминационной характеристики в цифровой частотный дискриминатор, содержащий входной амплитудный ограничитель, генератор опорного сигнала, два перемножителя, фазовращатель на π/2, первый знаковый триггер, триггер Шмидта, формирователь синхроимпульсов, блок управления, блок согласования времен отсчетов, регистр сдвига, N-разрядный реверсивный счетчик, элемент И, первый и второй n-входовые элементы И, управляющий триггер, элемент ИЛИ и реверсивный счетчик с ограничением счета с соответствующими связями, введен блок устранения дребезга, имеющий два входа, подключенные соответственно к выходам первого и второго перемножителей, второй выход блока устранения дребезга соединен с сигнальным входом блока согласования времени отсчетов, первый и второй выходы блока устранения дребезга подключены ко входам введенного блока усреднения знака, выход которого является выходом потенциала знака, в блок управления введен делитель частоты с изменяемым коэффициентом деления, вход которого подключен ко входу блока управления, а его выход подключен ко входу формирователя синхроимпульсов, а управляющие входы делителя частоты с изменяемым коэффициентом деления подключены к выходам реверсивного счетчика с ограничением счета, причем вход триггера Шмидта подключен к выходу входного амплитудного ограничителя, а его выход подключен ко вторым входам первого и второго перемножителей, также введен блок изменения формы дискриминационной характеристики, входы которого подключены к выходам реверсивного счетчика с ограничением счета, управляющие входы соединены с выходом первого знакового триггера и с прямыми выходами N-разрядного реверсивного счетчика, при этом выходы блока изменения формы дискриминационной характеристики являются выходами устройства. 7 ил.

|