|

На данной странице представлена ознакомительная часть выбранного Вами патента

Для получения более подробной информации о патенте (полное описание, формула изобретения и т.д.) Вам необходимо сделать заказ. Нажмите на «Корзину»

| УСТРОЙСТВО ДЛЯ РЕЗЕРВИРОВАНИЯ ЗАЩИТ ТЯГОВЫХ ПОДСТАНЦИЙ |  |

Номер публикации патента: 2183041 |  |

| Редакция МПК: | 7 | | Основные коды МПК: | H02H003/26 H02H003/28 H02H003/093 | | Аналоги изобретения: | SU 1304118 A1, 15.04.1987. SU 1081724 A, 23.03.1984. RU 2004041 C1, 30.11.1993. DE 1763424 B2, 28.10.1971. US 5243489 A, 07.09.1993. |

| Имя заявителя: | Дальневосточный государственный университет путей сообщения | | Изобретатели: | Дынькин Б.Е.

Пинчуков П.С. | | Патентообладатели: | Дальневосточный государственный университет путей сообщения |

Реферат |  |

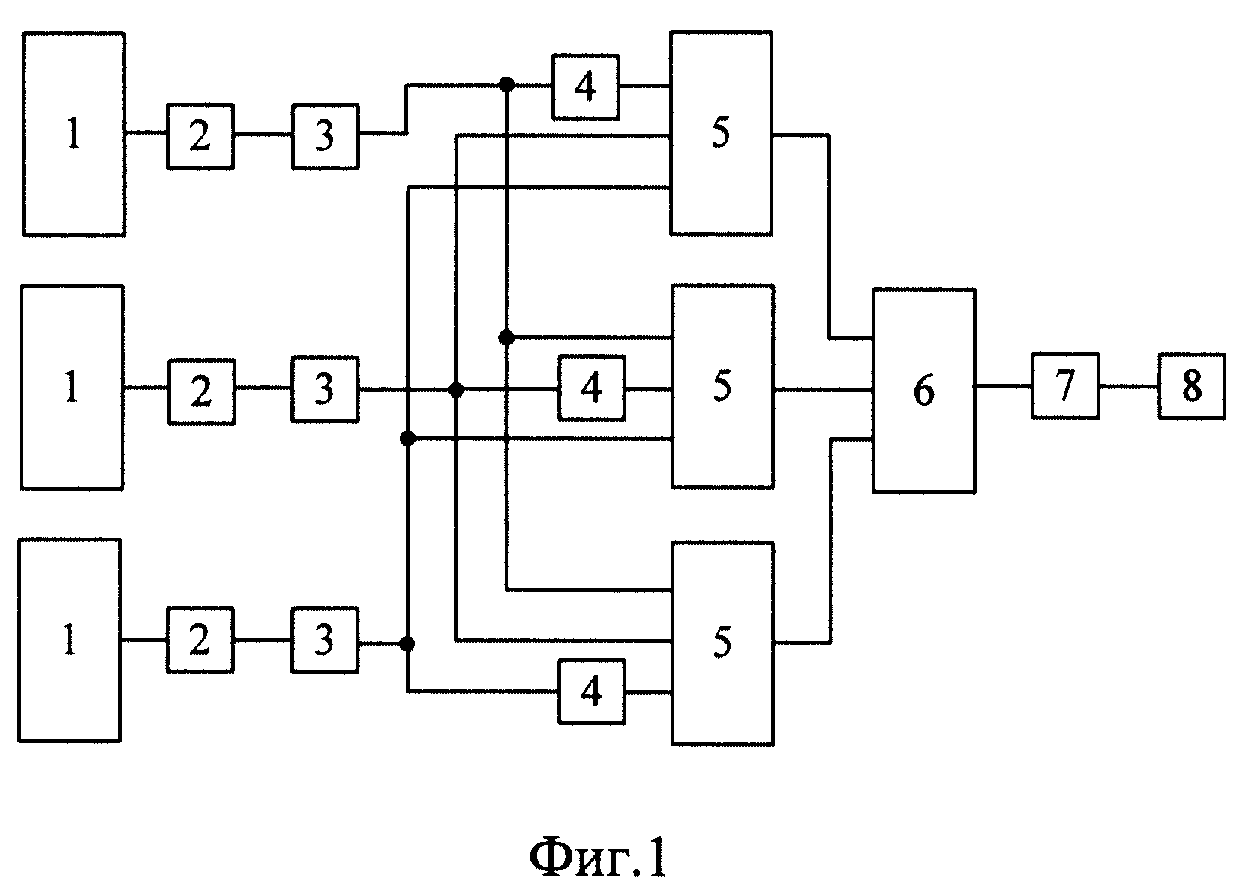

Изобретение относится к релейным защитам линий электропередачи, в частности для резервирования защит тяговых подстанций. Технический результат, направленный на создание устройства, имеющего достаточную чувствительность для надежного резервирования защит тяговых подстанций, достигается путем того, что в устройство для резервирования защит тяговых подстанций, содержащее три параллельных ветви, каждая из которых включает сумматор токов, пороговый элемент и логический элемент ИЛИ, реле времени, вход которого присоединен к выходу логического элемента ИЛИ и выход - к входу выходного элемента дополнительно введены три датчика приращения тока, три инвертора и три логических элемента И, при этом выход каждого сумматора токов соединен с входом соответствующего датчика приращения тока, выход которого соединен с входом соответствующего порогового элемента, выход каждого порогового элемента соединен через соответствующий инвертор с входом соответствующего логического элемента И и одним из входов двух других логических элементов И, выход каждого логического элемента И подключен к входу логического элемента ИЛИ. 4 ил.

|